Physical Layer Aspects of Storage Channels

Storage technologies have evolved from single/dual track tape drives to multi-track magnetic hard disks and multi-layered optical disk drives. With the need for higher storage densities, recording technologies are shifting from 1D towards two and higher dimensional paradigms. It is expected that storage technologies based on 2D magnetic recording (TDMR, bit patterned media), 3D flash memories and holographic recording will play a significant role as storage memories in desktops and enterprise servers to archival storage.

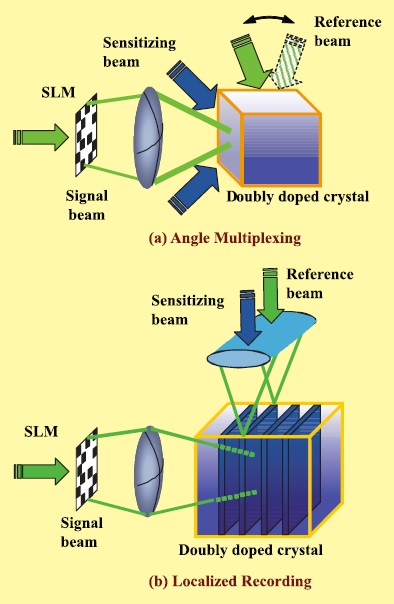

Figure 1: Holographic recording schemes: Angle multiplexing and localized holography. (a) In angle multiplexing, different holograms share the volume of the holographic medium. (b) In localized recording, each hologram is stored in a specific slice within the holographic material.

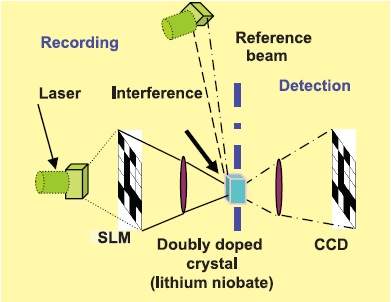

Figure 2: A volume holographic memory using angle multiplexing and 4F configuration. Digital data is modulated through the SLM, focused through the first lens and made to interfere coherently with a reference beam. The grated pattern is stored within a photo refractive material crystal such as LiNbO3. During detection, a reference beam at the original reference angle interferes with stored pattern; the reconstructed object beam is projected onto a CCD array for decoding the bits.

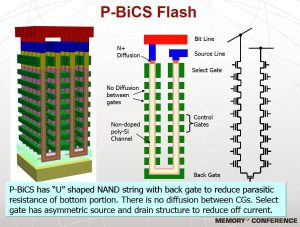

Figure 3: 3D Flash memory (p-BiCS technology) [Courtesy: Toshiba]

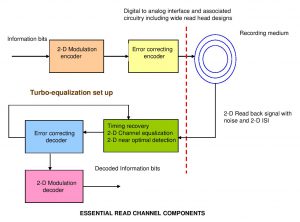

The physical core of storage technologies are the recording medium and read-write physics. The act of storing a bit and retrieving it reliably is an instance of a noisy communication. The read back signal suffers from intersymbol interference, noise and non-linear artifacts that need to be mitigated via advanced signal processing and coding. The tolerable code failure rates in physical memories are of the order 10-12. Also, the codes must be of high rate. This requires sophisticated coding techniques and signal processing algorithms (timing recovery, equalization, signal detection, non-linear compensation and data dependent noise prediction) to meet the demands. On the architectural side, it is important to realize algorithms that are aware of the physical constraints such as throughput, area and power.

At PNSIL, we focus on research involving the physical layer aspects of data storage channels as well as architectures that are aware of the algorithm and the channel constraints for novel memory technologies. Our tools involve fundamental/applied mathematics for algorithm development and VLSI circuits towards system architectures.

Past projects

- Timing recovery techniques and architectures for two dimensional storage channels

- Modeling, coding and signal processing for TDMR

Collaborations:

Indo-US Joint Networked Center for Data Storage Research:

- Shayan S. Garani (Chief PI)

- Navin Kashyap

- Bane Vasic (Chief PI)

- Paul Siegel

- John Barry

- Steve McLaughlin

Sponsors

- Department of Science and Technology (DST), India. Grant no. SERB/F/3371/2013-14.

- Department of Electronics and Information Technology (DeitY), India.

- Space Technology Cell, ISRO, India.

Journal Publications

- K. Bharadwaj and S. S. Garani, “Efficient Encoding Algorithm and Architecture for 2-D Quasicyclic LDPC Codes with Applications to 2-D Magnetic Recording,” in IEEE Transactions on Magnetics, doi: 10.1109/TMAG.2025.3603454.

- S. S. Garani and B. Vasic, “Channels Engineering in Magnetic Recording: From Theory to Practice,” in IEEE BITS Magazine, Nov. 2023.

- A. Mondal and S. S. Garani, “Efficient Parallel Decoding Architecture for Cluster Erasure Correcting 2-D LDPC Codes for Two-Dimensional Data Storage,” in IEEE Transactions on Magnetics, vol. 57, no. 12, pp. 1-16, December 2021.

- A. Mondal and S. S. Garani, “Efficient Parallel Decoding Architecture for Cluster Erasure Correcting 2-D LDPC Codes for Two-Dimensional Data Storage,” in IEEE Transactions on Magnetics, doi: 10.1109/TMAG.2021.3119723.

- A. Mondal and S. S. Garani, “Efficient Hardware Architectures for 2-D BCH Codes in the Frequency Domain for Two-Dimensional Data Storage Applications,” IEEE Trans. on Magn., doi: 10.1109/TMAG.2021.3060807.

- S. Roy and S. S. Garani, “Two-Dimensional Algebraic codes for Multiple Burst Error Correction”, IEEE Comm. Letters, vol. 23, no. 10, pp. 1684-1687, Oct. 2019.

- S. Roy, A. Mondal and S. S. Garani, “A Fast and Efficient Two-Dimensional Chien Search Algorithm and Design Architecture”, IEEE. Comm. Letters, vol. 23, no. 1, pp. 16-19, Jan. 2019.

- S. S. Garani, L. Dolecek, J. Barry, F. Sala and B. Vasic, “Signal Processing and Coding Techniques for 2-D Magnetic Recording: An Overview”, in Proc. of the IEEE., vol. 106, no. 2, pp. 286-318, Feb. 2018.

- A. Mondal, S. Thatimattala, V. K. Yalamaddi and S. S. Garani, “Efficient Coding Architectures for Reed-Solomon and Low-Density Parity-Check Decoders for Magnetic and Other Data Storage Systems,” in IEEE. Trans. Magn., vol. 54, no. 2, pp. 1-15, Feb. 2018.

- C. K. Matcha, S. Roy, M. Bahrami, B. Vasic and S. S. Garani, “2D LDPC Codes and Joint Detection and Decoding for Two-Dimensional Magnetic Recording,” IEEE. Trans. Magn., vol. 54, no. 2, Feb. 2018.

- C. K. Matcha and S. S. Garani, “Joint Timing Recovery and Signal Detection for Two-Dimensional Magnetic Recording,” IEEE. Trans. Magn., vol. 53, no. 2, Feb. 2017.

- C. K. Matcha and S. S. Garani, “Defect Detection and Burst Erasure Correction for TDMR,” in IEEE. Trans. Magn., vol. 52, no. 11, Nov. 2016.

- S. Datta and S. S. Garani, “Design Architecture of a Two-Dimensional Separable Iterative Soft Output Viterbi Detector,” in IEEE. Trans. Magn., vol.52, no. 1, Jan. 2016.

- C. K. Matcha and S. G. Srinivasa, “Generalized Partial Response Equalization and Data-Dependent Noise Predictive Signal Detection Over Media Models for TDMR,” in IEEE. Trans. Magn., vol. 51, no.10, pp.1-15, Oct. 2015.

- M. Bahrami, C. K. Matcha, S. M. Khatami, S. Roy, S. G. Srinivasa and B. Vasic, “Investigation into Harmful Patterns over Multi-Track Shingled Magnetic Detection Using the Voronoi Model,” in IEEE. Trans. Magn. vol. no. 99, pp.1-8, July 2015.

- B. P. Reddy, S. G. Srinivasa and S. Dahandeh “Timing Recovery Algorithms and Architectures for Two-Dimensional Magnetic Recording Systems,” in IEEE. Trans. Magn., Apr. 2015.

- S. G. Srinivasa, Y. Chen and S. Dahandeh “A communication-theoretic framework for TDMR channel modeling: Performance evaluation of coding and signal processing methods,” in IEEE. Trans. Magn., Mar. 2014.

- Y. Chen and S. G. Srinivasa “Joint Self-Iterating Equalization and Detection for Two-Dimensional Intersymbol-Interference Channels,” in IEEE. Trans. Comm., vol. 61, no. 8, pp. 3219-3230, Aug. 2013.

- S. G. Srinivasa, “Holographic Imaging: Information Recording and Retrieval,” Jour. Ind. Inst. Sci., vol. 93, no. 1, pp. 35-46, Mar. 2013. (Invited review article)

- S. G. Srinivasa, O. Momtahan, A. Karbaschi, S. W. McLaughlin, F. Fekri and A. Adibi, “Volumetric Storage Limits and Space Volume Multiplexing Trade-Offs for Holographic Channels,” in SPIE. Journal of Opt. Engineering, vol. 49, no. 1, Jan. 2010.

- S. G. Srinivasa and A. Weathers, “An Efficient on-the-fly Encoding Algorithm for Binary and Finite-Field LDPC Codes,” in IEEE. Comm. Lett., vol. 13, no. 11, pp. 853-855, Nov. 2009.

- S. G. Srinivasa and S. W. McLaughlin, “Capacity Bounds for Two-Dimensional Asymmetric M-ary (0,k) and (d,∞) Runlength-Limited Channels,” in IEEE. Trans. Comm., vol. 57, no. 6, pp. 1584-1587, June. 2009.

- S. G. Srinivasa, P. Lee and S. W. McLaughlin, “Post-Error Correcting Code Modeling of Burst Channels Using Hidden Markov Models with Applications to Magnetic Recording Channels,” in IEEE Trans. Magn., vol. 43, no. 2, pp. 572-579, Feb. 2007.

Patents

- Reed Solomon decoder and decoding methods, United States Patent No. 10,439,643, with S. Thattimattala and V. K. Yalamaddi, Sep. 2019.

- Method and apparatus for joint adaptation of two-/multi- dimensional equalizer and partial response target, Patent No. 10,026,441, with Chaitanya Kumar Matcha and Arnab Dey, Jul. 2018.

- Identifying a defect in a data-storage medium, United States Patent No. 9,324,370, with Sivagnanam Parthasarathy, 2016.

- Method and system for monitoring data channel to enable use of dynamically adjustable LDPC coding parameters in a data storage system, Patent No. 9,214,963, with Kent D. Anderson, Anantha Raman Krishnan, Guangming Lu, Shafa Dahandeh and Andrew J. Tomlin, Dec. 2015.

- Systems and methods for improved encoding of data in data storage devices, Patent No. 9,203,434, Shayan G. Srinivasa, Dec. 2015.

- Decoding data stored in solid-state memory, Patent No. 8,990,668, with Anantha Raman Krishnan and Kent Anderson, Mar. 2015.

- Data storage device tracking log-likelihood ratio for a decoder based on past performance, Patent No. 8,856,615, with Anantha Raman Krishnan, Kent Anderson and Shafa Dahandeh, Oct. 2014.

- Methods and devices for joint two-dimensional self-iterating equalization and detection, Patent No. 8,760,782, with Yiming Chen, June 2014.

- Constrained on-the-fly interleaver address generation, Patent No. 8,625,220, with Sivagnanam Parthasarathy and Sudha Thipparthi, Jan. 2014.

- Methods and devices for two-dimensional iterative multi-track based MAP detection, Patent No. 8,582,223, with Yiming Chen, Nov. 2013.

- Encoding apparatus, system and method using LDPC codes, Patent No. 8,397,125, Shayan G. Srinivasa, March. 2013.

- Adaptive data dependent noise prediction, Patent No. 8,290,102, with Mustafa Kaynak, Stefano Valle and Sivagnanam Parthasarathy, 2012.

- Interlaced iterative system design for 1K-byte block with 512 byte LDPC code words, Patent No. 8,255,768, with Xinde Hu, Sivagnanam Parthasarathy, Anthony Weathers and Richard Barndt, 2012.

- Channel constrained code aware interleavers, Patent No. 8,055,973, with Nicholas Richardson and Xinde Hu, 2011.

Conferences

- D. Shri, A. Mondal, and S. S. Garani, “An Improved Codec Design Architecture for Irregular LDPC Codes Applicable to WiMAX,” in IEEE Int. Conf. on Electron. Circ. and Sys. (ICECS), 2022.

- A. Mondal and S. S. Garani, “Efficient Hardware Design Architectures for BCH Product Codes in the Frequency Domain”, IEEE Intl. Midwest Symp. on Circuits and Syst. (MWSCAS), 2020.

- N. Raveendran, S. S. Garani and B. Vasic´, “An Improved Log-domain Belief Propagation Algorithm Over Graphs With Short Cycles” in Intl. Telemetry Conf., Las Vegas, 2019.

- C. K. Matcha, S. S. Garani, “2D Linear Detector Based on Generalized Belief Propagation Algorithm”, in Annual Allerton Conference on Communication, Control, and Computing (Allerton), Oct. 2018.

- A. B. Nair, A. Mondal, and S. S. Garani, “A Low-complexity Hardware AWGN Channel Emulator on FPGA using Central Limit Theorem” in IEEE Int. Midwest Symp. on Circuits and Syst, Windsor, Canada, Aug. 2018.

- S. Roy and S. S. Garani, “Two dimensional algebraic error correcting codes”, ITA, Feb. 2018.

- C. K. Matcha, S. Roy, M. Bahrami, B. Vasic and S. G. Srinivasa, “2D LDPC Codes and Joint Detection and Decoding for Two-Dimensional Magnetic Recording”, (2 page abstract) IEEE The Magn. Rec. Conf. (TMRC), Tsukuba, Japan, Aug. 2017. (Travel Award: IEEE Magn. Soc. Student Travel Grant.)

- A. Dey, S. Jose, K. Varghese, and S. G. Srinivasa, “A High-Throughput Clock-less Architecture for Soft-Output Viterbi Detection”, in IEEE International Midwest Symposium on Circuits and Systems, Boston, USA, Aug. 2017.

- C. K. Matcha, M. Bahrami, S. Roy, S. G. Srinivasa and B. Vasic, “Generalized Belief Propagation Based TDMR Detector and Decoder,” in IEEE. Proc. Intl. Symp. Inform. Theory, Barcelona, Spain, July 2016.

- E. Modak, B. Reddy and S. G. Srinivasa, “Optimum Timing Interpolation Algorithm for 2-D Magnetic Recording Systems” in IEEE Natl. Conf. Comm., Guwahati, India, Mar. 2016.

- S. Datta, K. Varghese, and S. G. Srinivasa, “A Non-uniformly Quantized High Throughput Soft Output Viterbi Detector on FPGA,” in IEEE Proc. VLSI, Kolkata, India, Jan. 2016.

- S. Roy and S. G. Srinivasa, “Two Dimensional Error-Correcting Codes using Finite Field Fourier Transform”, in IEEE Inf. Theory Work., ITW, Jeju Island, Oct. 2015.

- C. K. Matcha and S. G. Srinivasa, “A Study on the Implications of Grain Density Distribution over the Granular Media Model for TDMR,” in IEEE. Intl. Conf. on Magnetics (Intermag), Beijing, China, May 2015.

- C. K. Matcha and S. G. Srinivasa, “Exact Analysis of the Performance of Viterbi Detector for ISI Channels with Quantized Inputs,” in IEEE. National Conf. On Comm. (NCC), Mumbai, India, Mar. 2015.

- C. K. Matcha and S. G. Srinivasa, “Target Design and Low Complexity Signal Detection for Two Dimensional Magnetic Recording,” in IEEE. Asia-Pacific Signal and Inform. Proc. Conf., Siem Reap, city of Angkor Wat, Cambodia, Dec. 2014.

- C. K. Matcha, S. G. Srinivasa, S. M. Khatami and B. Vasic, “Two-Dimensional Noise-Predictive Maximum Likelihood Method for Magnetic Recording Channels,” in IEEE. Intl. Symp. Inform. Theory and Appl., Melbourne, Oct. 2014.

- B. P. Reddy, S. G. Srinivasa, and S. Dahandeh, “Timing Recovery Algorithms and Architectures for Two-Dimensional Magnetic Recording Systems,” in IEEE. Magn. Record. Conf., Berkeley, Aug. 2014.

- B. P. Reddy and S. G. Srinivasa, “Two-Dimensional Signal Processing for Timing Recovery Using PLLs for Storage Channels,” in IEEE. China Summit and Intl. Conf. Signal and Inform. Processing, Xi’an, July 2014.

- N. Raveendran and S. G. Srinivasa, “A Modified Sum-Product Algorithm Over Graphs with Isolated Short Cycles,” in IEEE. Proc. Intl. Symp. Inform. Theory, Honolulu, July 2014.

- N. Raveendran and S. G. Srinivasa, “An Analysis into the Loopy Belief Propagation Algorithm for Short Cycles,” in IEEE. Proc. Intl. Conf. on Comm., Sydney, June 2014.

- S. G. Srinivasa, “LDPC Code Designs Based on √I Matrices,” in IEEE. Inform. Theory Appl. Workshop, San Diego, Feb. 2014.

- S. G. Srinivasa, Y. Chen and S. Dahandeh, “A Communication-Theoretic Framework for TDMR Channel Modeling: Performance Evaluation of Coding and Signal Detection Methods,” in IEEE. Magn. Record. Conf., Tokyo, Aug. 2013.

- Y. Chen and S. G. Srinivasa, “Performance-Complexity Trade-Offs of the 2-D Iterative Feedback Signal Detection Algorithm,” in IEEE. Intl. Conf. Computing, Networking, and Communications, San Diego, Jan. 2013.

- A. Amiri, S. G. Srinivasa, and L. Dolecek, “Quantization, Absorbing Regions and Practical Message Passing Decoders,” in IEEE. Proc. Asilomar Conference, Monterey, Nov. 2012.

- Y. Chen and S. G. Srinivasa, “Signal Detection Algorithms for Two-Dimensional Intersymbol-Interference Channels,” in IEEE. Proc. Intl. Symp. Inform. Theory, Cambridge, July 2012.

- J. Zhang, J. Wang, S. G. Srinivasa, and L. Dolecek, “Achieving Flexibility in LDPC Code Design by Absorbing Set Elimination,” in IEEE. Proc. Asilomar Conference, Monterey, Nov. 2011.

- S. G. Srinivasa, O. Momtahan, A. Karbaschi, S. W. McLaughlin, A. Adibi, and F. Fekri, “M-ary, Binary, and Space-Volume Multiplexing Trade-Offs for Holographic Channels,” in IEEE. Proc. Globecomm, San Fransisco, Nov. 2006.

- S. G. Srinivasa and S. W. McLaughlin, “Capacity Lower Bounds for Two-Dimensional M-ary (d,∞) and (0,k) Runlength-Limited Channels,” in IEEE. Proc. Intl. Symp. Inform. Theory, Seattle, pp. 1472-1476, July 2006.

- S. G. Srinivasa, Patrick Lee and S. W. McLaughlin, “Post-ECC Modeling of Magnetic Recording Channels Using Hidden Markov Models,” in IEEE. Proc. Intl. Conf. on Comm., Istanbul, pp. 1249-1254, June 2006.

- S. G. Srinivasa and S. W. McLaughlin, “Capacity Bounds and Coding Schemes for Two-Dimensional Asymmetric k-constrained Runlength-Limited Arrays,” in Proc. Forty-third Allerton Conference on Computers, Control and Communications., Illinois Univ. Press, Monticello, IL-U.S.A., Oct. 2005.

- S. G. Srinivasa and S. W. McLaughlin, “Signal Recovery Due to Rotational Pixel Misalignment,” in IEEE. Proc. International Conference on Acoustics, Speech and Signal Processing, pp. 121-124, Philadelphia, U.S.A., Mar. 2005.

- S. G. Srinivasa and S. W. McLaughlin, “Enumeration Algorithms for a Class of (d1,∞,d2,∞) RLL arrays: Capacity Estimates and Coding Schemes,” in IEEE. Proc. Inform. Theory Workshop, pp. 141-146, San Antonio, U.S.A., Oct. 2004.

- S. G. Srinivasa and S. W. McLaughlin, “Algorithms for Constructing a Class of (1,∞ ,d,k) Codes and Estimates for Capacity,” in Proc. Forty-first Allerton Conference on Computers, Control and Communications., Illinois Univ. Press, pp. 867-875, Monticello, IL-U.S.A., Oct. 2003.