Neuromorphic Analog Circuit Design

Overview

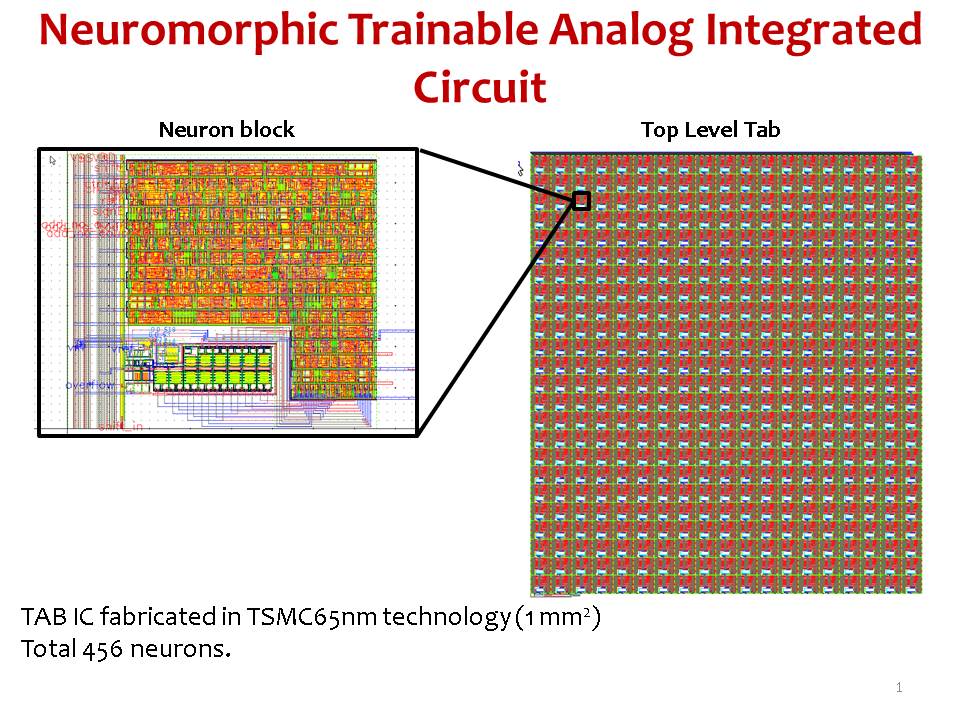

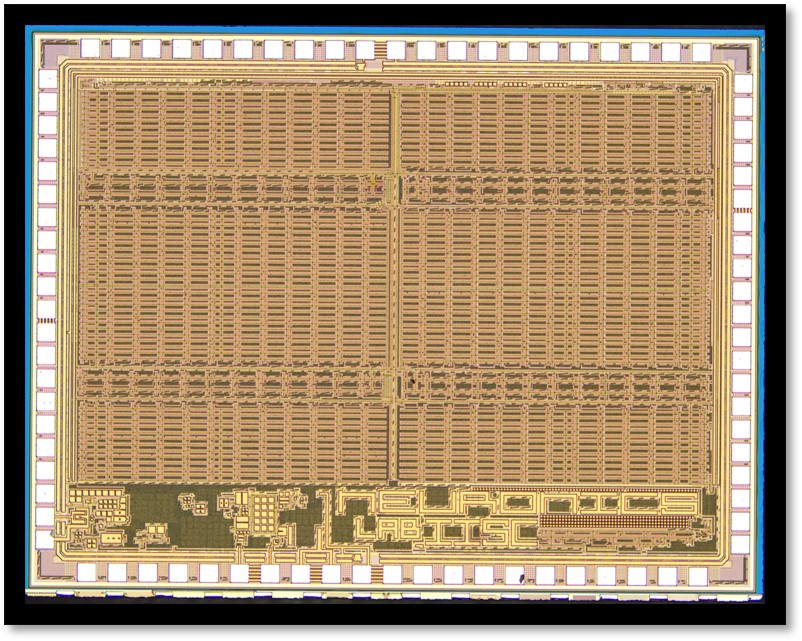

Our research theme is dedicated to developing brain-inspired computational models and next-generation neural networks and sensors. We implement these models using analog VLSI circuits to create real-time distributed neural processing systems for ultra-low power applications.

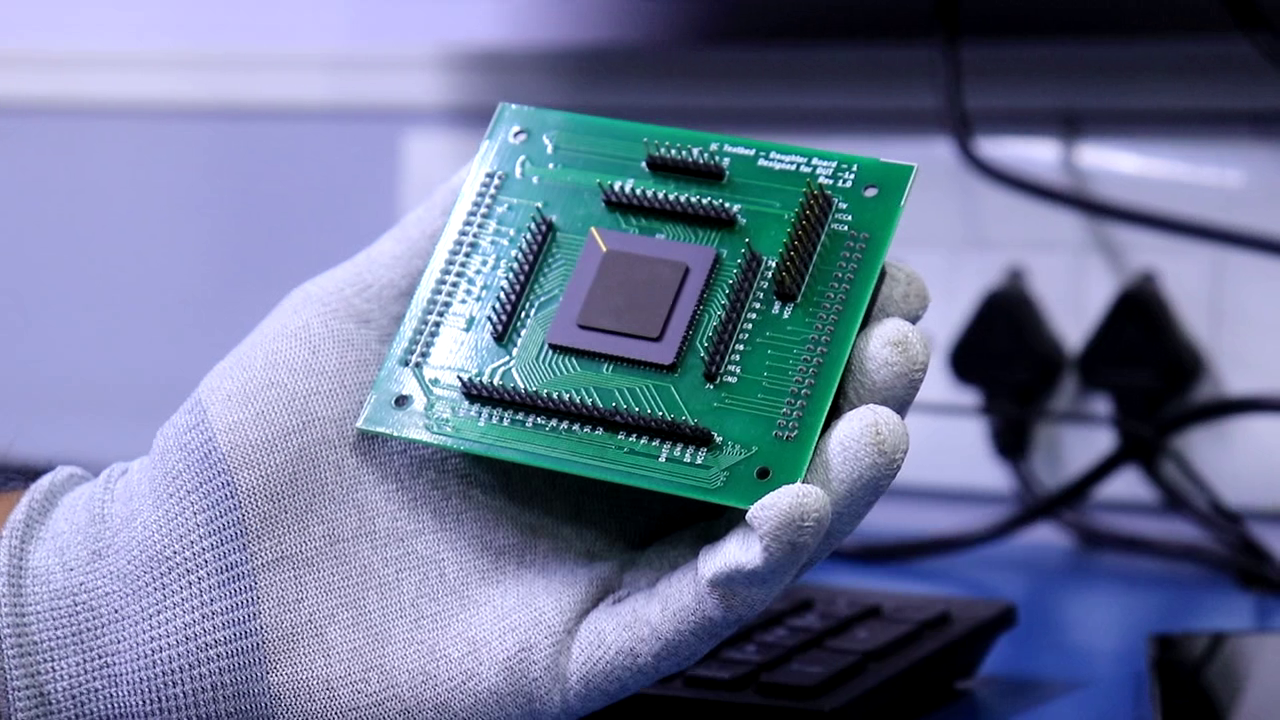

We have developed several chipsets such as Aryabhat, TAB, Silicon retina, and image sensors.

Aryabhat Chip

Demo Video: Aryabhat

Aryabhat is a programmable analog neural processor designed to support a wide range of machine learning models in ultra-low power edge devices. The video below demonstrates key features, real-time functionality, and application-specific use cases of the Aryabhat chip developed at the NeuRonICS Lab.

Watch on YouTubeSelected Publications

- Kumar, P., Nandi, A., Saha, A., Teja, K. S. P., Das, R., Chakrabartty, S., & Thakur, C. S. (2024). Aryabhat: A digital-like field programmable analog computing array for edge AI. IEEE Transactions on Circuits and Systems I: Regular Papers, 71(5), 2252–2265.

- Kumar, P., Nandi, A., Chakrabartty, S., & Thakur, C. S. (2023). Bias-scalable near-memory CMOS analog processor for machine learning. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 13(1), 312–322.

- Kumar, P., Nandi, A., Chakrabartty, S., & Thakur, C. S. (2022). Process, bias, and temperature scalable CMOS analog computing circuits for machine learning. IEEE Transactions on Circuits and Systems I: Regular Papers, 70(1), 128–141.

- Kumar, P., Zhu, K., Gao, X., Wang, S. D., Lanza, M., & Thakur, C. S. (2022). Hybrid architecture based on two-dimensional memristor crossbar array and CMOS integrated circuit for edge computing. npj 2D Materials and Applications, 6(1), 8.

- Gupta, S., Kumar, P., Paul, T., van Schaik, A., Ghosh, A., & Thakur, C. S. (2019). Low power, CMOS-MoS2 memtransistor based neuromorphic hybrid architecture for wake-up systems. Scientific Reports, 9(1), 15604.

- Thakur, C. S., Wang, R., Hamilton, T. J., Etienne-Cummings, R., Tapson, J., & van Schaik, A. (2017). An analogue neuromorphic co-processor that utilizes device mismatch for learning applications. IEEE TCAS-I, 65(4), 1174–1184.

- Thakur, C. S., Wang, R., Hamilton, T. J., Tapson, J., & van Schaik, A. (2016). A low power trainable neuromorphic integrated circuit that is tolerant to device mismatch. IEEE TCAS-I, 63(2), 211–221.

- Tharakan, A. T., Bhaskar, D., & Thakur, C. S. (2020). Implementation of Bayesian fly tracking model using analog neuromorphic circuits. In IEEE ISCAS 2020 (pp. 1–5).

- Zhang, J., Newman, J. P., Wang, X., Thakur, C. S., Rattray, J., Etienne-Cummings, R., & Wilson, M. A. (2020). A closed-loop, all-electronic pixel-wise adaptive imaging system for HDR videography. IEEE TCAS-I, 67(6), 1803–1814.

- Philip, P., Jainwal, K., van Schaik, A., & Thakur, C. S. (2023). Tau-cell-based analog silicon retina with spatio-temporal filtering and contrast gain control. IEEE TBioCAS, 18(2), 423–437.