Chip Gallery

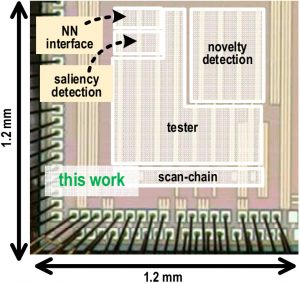

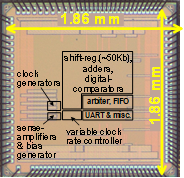

Novelty Detection Engine for DNN activity reduction

Technology: TSMC 40nm

Publications: VLSI’23

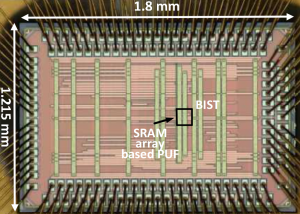

In-memory Physically Unclonable Function (PUF) version 2

Technology: TSMC 28nm

Publications: VLSI’23

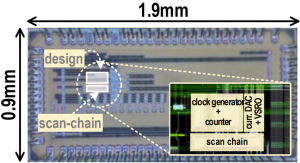

Digital impedance monitor for detection of power analysis attacks

Technology: TSMC 28nm

Publications: VLSI’22

Deep Neural Network (DNN) accelerator using Dyadic Digital Pulse Modulation (DDPM)

Technology: TSMC 40nm

Publications: CICC’22

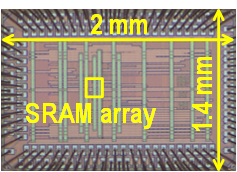

In-Memory-Computing Static Random Access Memory (SRAM)

Technology: TSMC 28nm

Publications: ESSCIRC’21

Electronic-skin interface

Technology: TSMC 40nm

Publications: VLSI’21

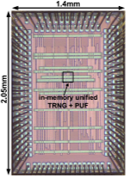

In-Memory True Random Number Generator (TRNG) and Physically Unclonable Function (PUF)

Technology: TSMC 28nm

Publications: ISSCC’21, JSSC’22

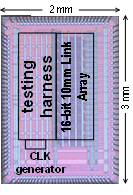

Energy quality scalable on-chip links

Technology: TSMC 28nm

Publications: CICC’19, JSSC’21

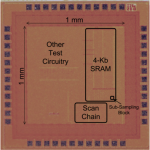

Fastest Ultra Dynamic voltage Scalable (U-DVS) Static Random Access Memory (SRAM)

Technology: UMC 130nm

Publications: ISSCC’15 (SRP), TVLSI’16