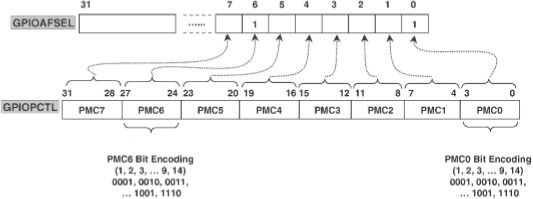

The digital alternate hardware functions are enabled by setting the appropriate bit in the GPIO Alternate Function Select (GPIOAFSEL) and configuring the PMCx bit field in the GPIO Port Control (GPIOPCTL) register.

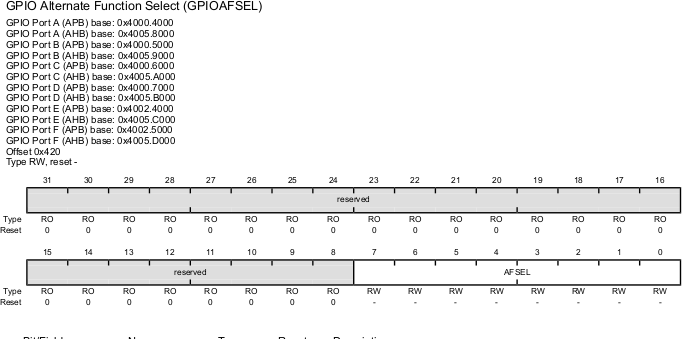

GPIO Alternate Function Select (GPIOAFSEL)

- The GPIOAFSEL register is the mode control select register. If a bit is clear, the pin is used as a GPIO and is controlled by the GPIO registers.

- Setting a bit in this register configures the corresponding GPIO line to be controlled by an associated peripheral.

- If an alternate pin is chosen for a bit, then the PMCx field must be programmed in the GPIOPCTL register for the specific peripheral required.

- Pin muxing options are provided through the GPIO Port Control (GPIOPCTL) register which selects one of several peripheral functions for each GPIO.

| Bit/Field | Name | Description |

|---|---|---|

| 7:0 | AFSEL | GPIO Alternate Function Select 0: The associated pin functions as a GPIO and is controlled by the GPIO registers. 1: The associated pin functions as a peripheral signal and is controlled by the alternate hardware function. |

| 31:8 | Reserved | Software should not rely on the value of a reserved bit. |

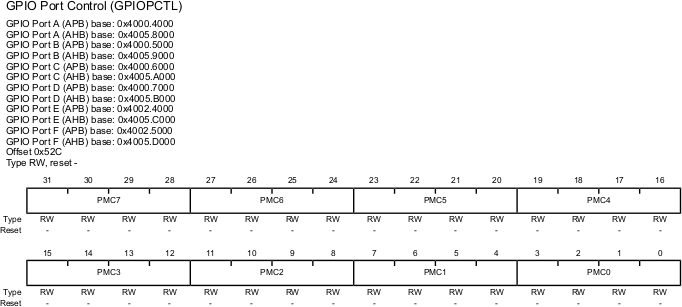

The GPIOPCTL register is used in conjunction with the GPIOAFSEL register and selects the specific peripheral signal for each GPIO pin when using the alternate function mode. When a bit is set in the GPIOAFSEL register, the corresponding GPIO signal is controlled by an associated peripheral. The GPIOPCTL register selects one out of a set of peripheral functions for each GPIO, providing additional flexibility in signal definition. Most bits in the GPIOAFSEL register are cleared on reset, therefore most GPIO pins are configured as GPIOs by default.

| Bit/Field | Name | Description |

|---|---|---|

| 3:0 | PMC0 | Port Mux Control 0 This field controls the configuration for GPIO pin 0 |

| 7:4 | PMC1 | Port Mux Control 1 This field controls the configuration for GPIO pin 1 |

| 11:8 | PMC2 | Port Mux Control 2 This field controls the configuration for GPIO pin 2 |

| 15:12 | PMC3 | Port Mux Control 3 This field controls the configuration for GPIO pin 3 |

| 19:16 | PMC4 | Port Mux Control 4 This field controls the configuration for GPIO pin 4 |

| 23:20 | PMC5 | Port Mux Control 5 This field controls the configuration for GPIO pin 5 |

| 27:24 | PMC6 | Port Mux Control 6 This field controls the configuration for GPIO pin 6 |

| 31:28 | PMC7 | Port Mux Control 7 This field controls the configuration for GPIO pin 7 |

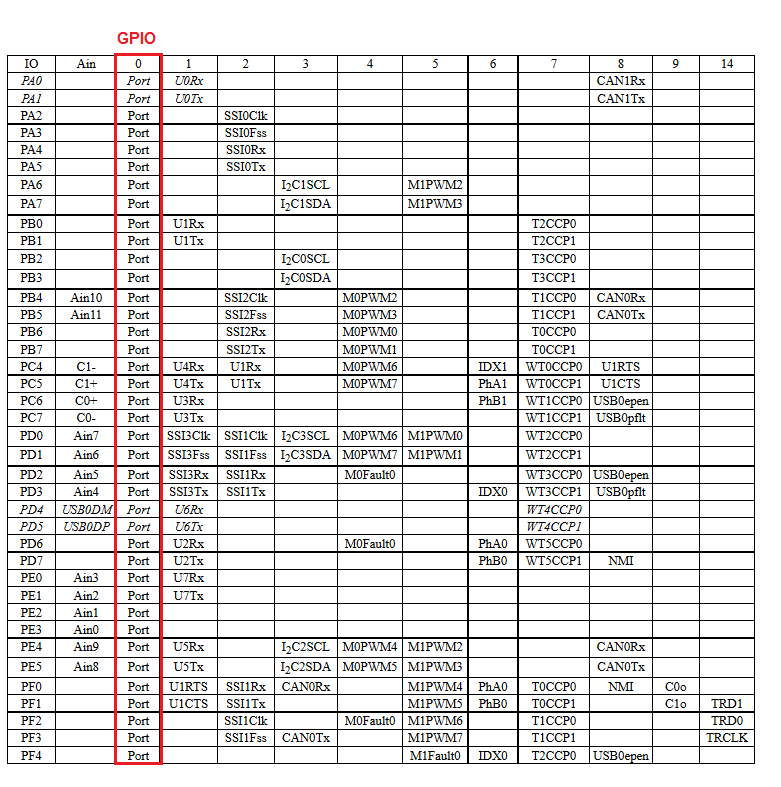

Figure: GPIO Pins and Alternate Functions

Recent Comments