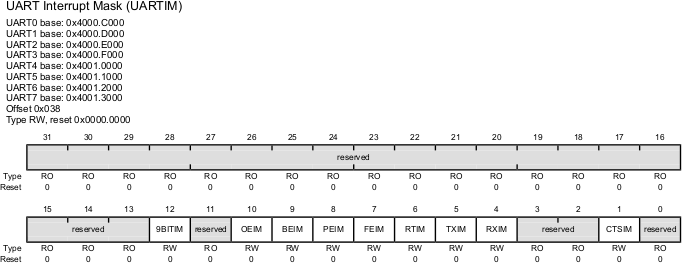

Examining the UARTIM (UART Interrupt Mask) register, we see bit 4 allows us to enable the receive interrupt. If the receive interrupt for UART is enabled, when a byte is received, the receive flag is directed to NVIC and that causes the interrupt handler associated with the UART to be executed. In the UART handler we must read the received byte and clear the interrupt flag.

UART Interrupt Mask Register

| bit | Name | Description |

|---|---|---|

| 1 | CTSIM | UART Clear to Send Modem Interrupt Mask 1: An interrupt is sent to the interrupt controller when the CTSRIS bit in the UARTRIS register is set. 0: The CTSRIS interrupt is suppressed and not sent to the interrupt controller. |

| 4 | RXIM | UART Receive Interrupt Mask 1: An interrupt is sent to the interrupt controller when the RXRIS bit in the UARTRIS register is set. 0: The RXRIS interrupt is suppressed and not sent to the interrupt controller. |

| 5 | TXIM | UART Transmit Interrupt Mask 1: An interrupt is sent to the interrupt controller when the TXRIS bit in the UARTRIS register is set. 0: The TXRIS interrupt is suppressed and not sent to the interrupt controller. |

| 6 | RTIM | UART Receive Time-Out Interrupt Mask 1: An interrupt is sent to the interrupt controller when the RTRIS bit in the UARTRIS register is set 0: The RTRIS interrupt is suppressed and not sent to the interrupt controller. |

| 7 | FEIM | UART Framing Error Interrupt Mask 1: An interrupt is sent to the interrupt controller when the RTRIS bit in the UARTRIS register is set. 0: The FERIS interrupt is suppressed and not sent to the interrupt controller. |

| 8 | PEIM | UART Parity Error Interrupt Mask 1: An interrupt is sent to the interrupt controller when the PERIS bit in the UARTRIS register is set. 0: The PERIS interrupt is suppressed and not sent to the interrupt controller. |

| 9 | BEIM | UART Break Error Interrupt Mask 1: An interrupt is sent to the interrupt controller when the BERIS bit in the UARTRIS register is set. 0: The BERIS interrupt is suppressed and not sent to the interrupt controller. |

| 10 | OEIM | UART Overrun Error Interrupt Mask 1: An interrupt is sent to the interrupt controller when the OERIS bit in the UARTRIS register is set. 0: The OERIS interrupt is suppressed and not sent to the interrupt controller. |

| 12 | 9BITIM | 9-Bit Mode Interrupt Mask 1: An interrupt is sent to the interrupt controller when the 9BITRIS bit in the UARTRIS register is set. 0: The 9BITRIS interrupt is suppressed and not sent to the interrupt controller. |

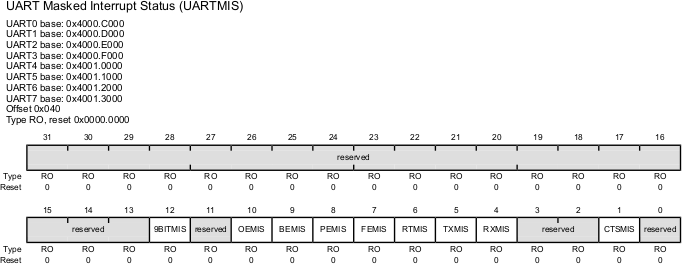

UART Masked Interrupt Status (UARTMIS)

| bit | Name | Value Description |

|---|---|---|

| 1 | CTSMIS | UART Clear to Send Modem Masked Interrupt Status 1: An unmasked interrupt was signaled due to Clear to Send. 0: An interrupt has not occurred or is masked. |

| 4 | RXMIS | UART Receive Masked Interrupt Status 1: An unmasked interrupt was signaled due to passing through the specified receive FIFO level. 0: An interrupt has not occurred or is masked. |

| 5 | TXMIS | UART Transmit Masked Interrupt Status 1: An unmasked interrupt was signaled due to passing through the specified transmit FIFO level (if the EOT bit is clear) or due to the transmission of the last data bit (if the EOT bit is set). 0: An interrupt has not occurred or is masked. |

| 6 | RTMIS | UART Receive Time-Out Masked Interrupt Status 1: An unmasked interrupt was signaled due to a receive time out. 0: An interrupt has not occurred or is masked. |

| 7 | FEMIS | UART Framing Error Masked Interrupt Status 1: An unmasked interrupt was signaled due to a framing error. 0: An interrupt has not occurred or is masked. |

| 8 | PEMIS | UART Parity Error Masked Interrupt Status 1: An unmasked interrupt was signaled due to a parity error. 0: An interrupt has not occurred or is masked. |

| 9 | BEMIS | UART Break Error Masked Interrupt Status 1: An unmasked interrupt was signaled due to a break error. 0: An interrupt has not occurred or is masked. |

| 10 | OEMIS | UART Overrun Error Masked Interrupt Status 1: An unmasked interrupt was signaled due to an overrun error. 0: An interrupt has not occurred or is masked. |

| 12 | 9BITMIS | 9-Bit Mode Masked Interrupt Status 1: An unmasked interrupt was signaled due to a receive address match. 0: An interrupt has not occurred or is masked. |

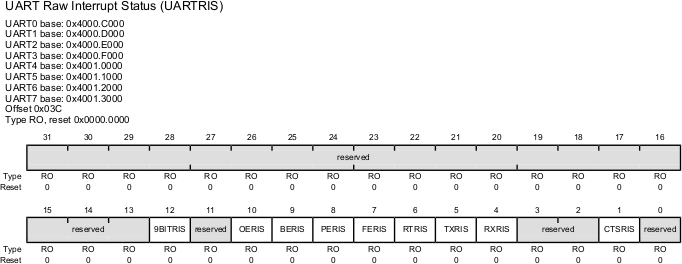

UART Raw Interrupt Status (UARTRIS)

| bit | Name | Description |

|---|---|---|

| 1 | CTSRIS | UART Clear to Send Modem Raw Interrupt Status 1: Clear to Send used for software flow control. 0: No interrupt |

| 4 | RXRIS | UART Receive Raw Interrupt Status 1: The receive FIFO level has passed through the condition defined in the UARTIFLS register. 0: No interrupt |

| 5 | TXRIS | UART Transmit Raw Interrupt Status 1: If the EOT bit in the UARTCTL register is clear, the transmit FIFO level has passed through the condition defined in the UARTIFLS register. If the EOT bit is set, the last bit of all transmitted data and flags has left the serializer. 0: No interrupt |

| 6 | RTRIS | UART Receive Time-Out Raw Interrupt Status 1: A receive time out has occurred. 0: No interrupt |

| 7 | FERIS | UART Framing Error Raw Interrupt Status 1: A framing error has occurred. 0: No Interrupt |

| 8 | PERIS | UART Parity Error Raw Interrupt Status 1: A parity error has occurred. 0: No Interrupt. |

| 9 | BERIS | UART Break Error Raw Interrupt Status 1: A break error has occurred. 0: No Interrupt. |

| 10 | OERIS | UART Overrun Error Raw Interrupt Status 1: An overrun error has occurred. 0: No Interrupt. |

| 12 | 9BITRIS | 9-Bit Mode Raw Interrupt Status 1: A receive address match has occurred. 0: No Interrupt. |

UART Interrupt Clear (UARTICR)

| bit | Name | Description |

|---|---|---|

| 1 | CTSMIC | UART Clear to Send Modem Interrupt Clear Writing a 1 to this bit clears the CTSRIS bit in the UARTRIS register and the CTSMIS bit in the UARTMIS register. This bit is implemented only on UART1 and is reserved for UART0 and UART2. |

| 4 | RXIC | Receive Interrupt Clear Writing a 1 to this bit clears the RXRIS bit in the UARTRIS register and the RXMIS bit in the UARTMIS register. |

| 5 | TXIC | Transmit Interrupt Clear Writing a 1 to this bit clears the TXRIS bit in the UARTRIS register and the TXMIS bit in the UARTMIS register. |

| 6 | RTIC | Receive Time-Out Interrupt Clear Writing a 1 to this bit clears the RTRIS bit in the UARTRIS register and the RTMIS bit in the UARTMIS register. |

| 7 | FEIC | Framing Error Interrupt Clear Writing a 1 to this bit clears the FERIS bit in the UARTRIS register and the FEMIS bit in the UARTMIS register. |

| 8 | RTIC | Parity Error Interrupt Clear Writing a 1 to this bit clears the PERIS bit in the UARTRIS register and the PEMIS bit in the UARTMIS register. |

| 9 | BEIC | Break Error Interrupt Clear Writing a 1 to this bit clears the BERIS bit in the UARTRIS register and the BEMIS bit in the UARTMIS register. |

| 10 | OEIC | Overrun Error Interrupt Clear Writing a 1 to this bit clears the OERIS bit in the UARTRIS register and the OEMIS bit in the UARTMIS register. |

| 12 | 9BITIC | 9-Bit Mode Interrupt Clear Writing a 1 to this bit clears the 9BITRIS bit in the UARTRIS register and the 9BITMIS bit in the UARTMIS register. |

Recent Comments